Chip Atomic Clock vs VCSEL: What VCSEL Manufacturers Should Know

Why this topic matters to a VCSEL maker

Precise timing drives modulation accuracy, phase control, and ranging precision in VCSEL arrays.

Better clocks mean cleaner eye diagrams, lower BER, tighter TOF windows, and more repeatable FMCW chirps.

Customers evaluating VCSEL modules increasingly ask about reference clocking, holdover, and phase-noise budgets. Being fluent in CSAC integration helps you win design-ins.

Definitions (plain English)

What is a chip-scale atomic clock (CSAC)?

A CSAC is a palm-sized atomic reference (typically rubidium) that outputs a highly stable frequency (commonly 10 MHz) and/or PPS for long-term accuracy and holdover. It outperforms TCXO/OCXO when drift, temperature swings, or GPS-denied operation are concerns.

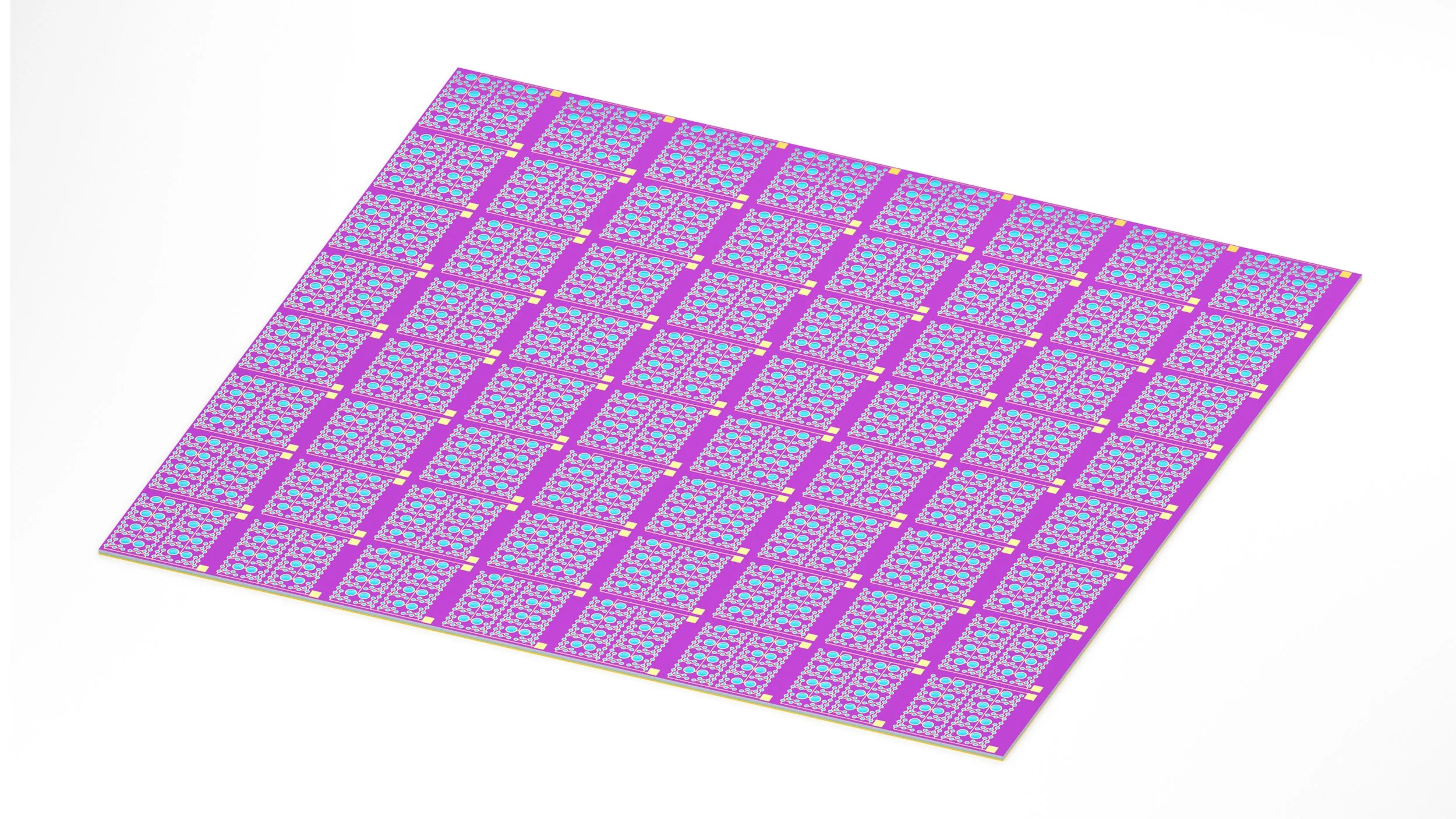

What is a VCSEL?

A vertical-cavity surface-emitting laser that emits perpendicular to the wafer surface. VCSELs are efficient, array-friendly, and ideal for 3D sensing/ToF, industrial ranging, consumer proximity sensing, and short-reach data links (e.g., 850–940 nm).

The real question behind “Chip atomic clock vs VCSEL”

You don’t choose one instead of the other. You choose whether your VCSEL system should be disciplined by a CSAC (vs TCXO/OCXO/GNSS). The decision hinges on timing stability, jitter, environmental robustness, and holdover requirements.

Where CSACs lift VCSEL-based performance

1) Time-of-Flight (ToF) and structured-light 3D sensing

Tighter timing windows → better depth precision and less range drift.

Consistent modulation frequencies across temperature and lifetime improve multi-sensor fusion and factory calibration yield.

2) FMCW LiDAR using VCSEL arrays

Chirp linearity and repeatability depend on the reference.

Array phase coherence and inter-frame stability benefit from an ultra-stable 10 MHz master.

3) Short-reach optical links (AOCs, data center interconnects)

The CSAC can discipline a PLL/CDR that drives the VCSEL, improving jitter tolerance and BER margins in harsh environments or GNSS-denied sites.

4) Industrial/medical instrumentation

Metrology and imaging that rely on modulated VCSELs gain repeatable calibration and lower drift, cutting re-zeroing and field returns.

CSAC vs TCXO/OCXO/GNSS: how to choose for VCSEL designs

Key takeaway: If your VCSEL module ships into GNSS-denied, high-vibration, or wide-temperature use cases—or if range repeatability and chirp integrity are selling points—CSAC is your safest bet.

Design checklist: integrating a CSAC into a VCSEL platform

Clock tree architecture

Use the CSAC’s 10 MHz as the single source of truth. Fan out via low-jitter buffers into the PLL that generates your VCSEL modulation/carrier.

Keep a clean PPS path if you timestamp frames or align multiple sensors.

Phase-noise and jitter budgeting

Budget end-to-end from CSAC → PLL/CDR → VCSEL driver → optical path.

Validate with phase-noise masks and period-jitter at operating frequencies (tens of MHz for ToF, ramp bands for FMCW).

Power & thermal

CSACs draw more power than TCXOs. Provide quiet rails, local LDOs, and thermal isolation to prevent drift coupling into the VCSEL die or NTC loop.

Holdover strategy

If GNSS is used at build-time or intermittently, let the CSAC maintain holdover. Log drift over life to support predictive maintenance.

EMI/layout

Short, guarded clock traces; 50 Ω controlled impedance on high-speed lines; avoid injecting spurs into the VCSEL driver bias network.

Factory calibration

Calibrate modulation frequency, phase alignment (arrays), and ToF zero-offset with the CSAC locked. Store trims in NVM.

Benefits you can market (and measure)

Lower range error and better depth repeatability in ToF and LiDAR demos.

Cleaner eye diagrams and BER headroom in demo boards and eval kits.

Reduced re-calibration across temperature cycling and product life.

Consistent multi-sensor synchronization (PPS-aligned frames across modules).

Common buyer questions (fast answers)

Do all VCSEL products need a chip atomic clock?

No. Many consumer modules ship with TCXO/OCXO. Choose CSAC when holdover, drift, and harsh environments are critical.Will a CSAC fix poor driver design?

No clock can rescue a noisy driver or layout. You still need proper filtering, bias control, and layout discipline.Can we start with TCXO and upgrade later?

Yes—if you design the clock tree and power budget up front. Keep footprints/power headers compatible.

Example architectures

A. ToF/Structured-light VCSEL module (CSAC-disciplined)

CSAC 10 MHz → Low-jitter buffer → PLL (modulation frequency) → VCSEL driver → VCSEL array

PPS → Time-stamper / MCU for frame alignment

B. FMCW LiDAR VCSEL array (CSAC-disciplined)

CSAC 10 MHz → Chirp synthesizer/PLL → Current driver with linear ramp control → VCSEL array

PPS → Sensor fusion / navigation clock domain

From the manufacturer’s bench: how we support CSAC options

As a VCSEL producer, we offer:

Clocking variants: footprints for TCXO/OCXO/CSAC and compatible headers.

Reference designs: phase-noise-optimized PLL chains and EMI-aware layouts.

Calibration scripts: automated modulation trim and ToF zeroing with CSAC lock.

Environmental validation: temperature cycling and vibration with holdover logging.

Want a CSAC-ready VCSEL module or array? We can deliver CSAC-disciplined driver boards, plus documentation for your compliance team.

Conclusion

“Chip atomic clock vs VCSEL” isn’t a versus—it’s a value stack. A CSAC provides the ultra-stable heartbeat; the VCSEL turns that stability into range accuracy, cleaner links, and repeatable sensing. If your customers care about precision, harsh-environment stability, and holdover, shipping a CSAC-disciplined VCSEL solution can be the difference between a demo and a design win.